19th International Symposium on Computer Architecture

and High Performance Computing

SBAC-PAD 2007 Awards

Click here to see the awards results of the conference.

Program:

The SBAC-PAD Conference Program is available. Print version available here.

SBAC-PAD 2007 Workshops

Click here to get the workshops that will happen during the conference.

Parallel Programming:

You can check the updated rules and awards of the Marathon and the already started Open Contest. In order to submit your proposal for the Open Contest, click here.

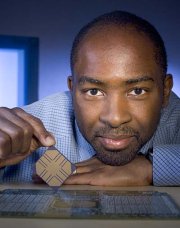

Featured Photo:

Previous Editions:

Click here for previous editions of SBAC-PAD and to access their conference proceedings.

Keynotes

These are the keynotes confirmed for SBAC-PAD 2007.Keynote #1: The Datacenter as a Computer

Luiz André Barroso, Google Inc., USA

Abstract: The computing systems that are powering many of today's large-scale Internet services look less like refrigerators and more like warehouses. Designing efficient warehouse-scale computers requires many of the traditional tools and methods developed by computer architects, and some new tricks as well. In this talk I'll describe some of the defining characteristics of these systems, with a focus on failure handling and power management.

Bio: Luiz André Barroso is a Distinguished Engineer at Google, where he has worked across several engineering areas, ranging from applications and software infrastructure to hardware design. Prior to working at Google, he was a member of the Research Staff at Compaq and Digital Equipment Corporation, where his group did some of the pioneering work on computer architectures for commercial workloads. That work included the design of Piranha, a system based on an aggressive chip-multiprocessing, which helped inspire many of the multi-core CPUs that are now in the mainstream. Luiz has a Ph.D. degree in computer engineering from the University of Southern California and B.S. and M.S. degrees in electrical engineering from the Pontifícia Universidade Católica, Rio de Janeiro.

Keynote #2: Democratizing Parallel Software Development

Kunle Olukotun, Stanford University, USA

Abstract: Now that we are firmly entrenched in the multicore era, to increase software functionality without decreasing performance many application developers will have to become parallel programmers. Today, parallel programming is so difficult the that it is only practiced by a few elite programmers. Thus, a key research question is what set of hardware and software technologies will make parallel computation accessible to average programmers. In this talk I will describe a set of architecture and programming language techniques that have the potential to dramatically simplify the task of writing a parallel program.

Bio: Kunle Olukotun has been a Professor of Electrical Engineering and ComputerScience at Stanford University where he has been on the faculty since 1991. Olukotun has been a researcher in and proponent of Chip Multiprocessor technology since the early 1990's. Olukotun is well known for leading the Stanford Hydra research project which developed one of the first chip multiprocessors with support for thread-level speculation (TLS). Olukotun founded Afara Websystems to develop high- throughput, low power server systems with chip multiprocessor technology. Afara was acquired by Sun Microsystems; the Afara microprocessor technology, called Niagara, is at the center of Sun's throughput computing initiative. Niagara based systems have become one of Sun's fastest ramping products ever. Olukotun is actively involved in research in computer architecture, parallel programming environments and scalable parallel systems. Olukotun currently coleads the Transactional Coherence and Consistency project whose goal is to make parallel programming accessible to average programmers. Olukotun also directs the Stanford Pervasive Parallelism Lab (SPPL) which seeks to proliferate the use of parallelism in all application areas. Olukotun is an ACM Fellow (2006) for contributions to multiprocessors on a chip and multi threaded processor design. He has authored many papers on CMP design and parallel software and recently completed a book on CMP architecture. Olukotun received his Ph.D. in Computer Engineering from The University of Michigan.

Keynote #3: Petascale and Multicore Programming Models: What is needed

Laxmikant (Sanjay) Kale, University of Illinois at Urbana-Champaign, USA

Abstract: The almost simultaneous emergence of multicore chips and petascale computers presents multidimensional challenges and opportunities for parallel programming. What kind of programming models will prevail? What are some of the required and desired characteristics of such model/s? I will attempt to answer these questions. My answers are based in part on my experience with several applications ranging from quantum chemistry, biomolecular simulations, simulation of solid propellant rockets, and computational astronomy.

Bio: Laxmikant (Sanjay) Kale is a Professor in the Department of Computer Science, University of Illinois at Urbana-Champaign. His research interests span tools and techniques for parallel programming and its applications. His focus is on methods for improving programmer productivity and parallel performance for complex parallel applications. He participates in several collaborative projects with researchers in science and engineering. A paper he co-authored on scaling molecular dynamics for biomolecular simulations received a Gordon Bell Award in SC'2002. Kale received the B.Tech degree in Electronics Engineering from Benares Hindu University, Varanasi, India in 1977, and a M.E. degree in Computer Science from Indian Institute of Science in Bangalore, India, in 1979. He received a Ph.D. in computer science from State University of New York, Stony Brook, in 1985.

| Co-sponsored by TCCA and TCSC of |

and | Conference Proceedings are published by |

Promoted by | Organized by |

|

|

|

|

|

| Sponsors | ||||

|

||||