# Estudo sobre o Impacto do Processador Hospedeiro no Desempenho das Arquiteturas Reconfiguráveis Híbridas

Alba S. Bezerra Lopes, Miklécio Bezerra da Costa, Monica M. Pereira, Ivan Saraiva Silva¹

Departamento de Informática e Matemática Aplicada

Universidade Federal do Rio Grande do Norte, Natal, Brasil

(alba, miklecio, monica)@natalnet.br, ivan@dimap.ufrn.br¹

### Resumo

Esse artigo apresenta um estudo que relaciona a escolha do processador hospedeiro com o desempenho das arquiteturas reconfiguráveis híbridas. Como estudo de caso foram comparados os processadores Nios II e SPARC V8, para avaliar o processador mais adequado para a arquitetura reconfigurável RoSA. Os resultados mostraram que foi possível alcançar até 47% de ganho com o uso do processador Nios II em comparação ao SPARC V8.

## 1. Introdução

Existem duas abordagens tradicionais de arquiteturas de computadores. A primeira corresponde aos processadores de propósito geral, também conhecidos como arquiteturas de Von Neumman. Esses dispositivos são caracterizados por possuírem um alto grau de flexibilidade e, portanto, são capazes de realizar qualquer tipo de computação.

A segunda abordagem corresponde aos dispositivos de propósito específico, conhecidos como ASICs (do inglês *Application Specific Integrated Circuits*). Estes dispositivos são direcionados à execução de um número restrito de computações ou até mesmo de uma única tarefa. Quando comparados observa-se que a primeira supera a segunda em flexibilidade e perde em desempenho [1].

Com o objetivo de prover uma solução que faça uso da flexibilidade propiciada pelos processadores de propósito geral e do alto desempenho dos ASICs, surgiram as arquiteturas reconfiguráveis. Nesta abordagem, os dispositivos são capazes de adaptar e modificar suas estruturas de hardware de acordo com as necessidades da aplicação.

A maioria das arquiteturas reconfiguráveis existentes trabalha como co-processador. Essa

estrutura, composta de um processador hospedeiro e um ou mais blocos reconfiguráveis, é chamada de arquitetura reconfigurável híbrida.

Na literatura podem ser encontradas diversas propostas de arquiteturas híbridas [2]. A maioria dos trabalhos publicados concentra-se no projeto do bloco reconfigurável, ou na adaptação e execução de aplicações. Entretanto, pouco se publicou sobre o impacto do processador a ser anexado à lógica reconfigurável. Dessa forma, a escolha do processador geralmente é feita sem qualquer conhecimento sobre sua adequabilidade ao projeto.

Este artigo propõe um estudo sobre o impacto que o processador hospedeiro causa no projeto de arquiteturas reconfiguráveis híbridas. Como estudo de caso são comparados os processadores SPARC V8 da Sun Microsystems [3] e Nios II da Altera [4]. O objetivo do estudo é obter dados suficientes para fazer opção pelo uso de um dos processadores. O processador selecionado será anexado à arquitetura reconfigurável denominada RoSA.

RoSA é uma arquitetura reconfigurável híbrida de granularidade grossa voltada para a exploração de paralelismo a nível de instrução de aplicações baseadas em fluxo de dados [5].

Esse artigo está organizado da seguinte forma: a seção 2 apresenta uma visão geral sobre a arquitetura RoSA. Na seção 3 são apresentadas as principais características dos processadores estudados. A seção 4 apresenta os resultados sobre o desempenho dos processadores. Por fim, na seção 5 é apresentada a conclusão.

# 2. Arquitetura Reconfigurável RoSA

RoSA (do inglês *Reconfigurable Stream-based Architecture*) é uma arquitetura reconfigurável de granularidade grossa que explora o paralelismo a nível de instrução de aplicações baseadas em fluxo de dados

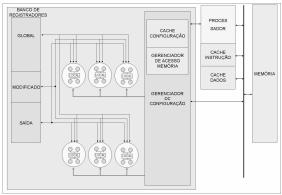

[5]. A Figura 1 apresenta o diagrama de blocos da arquitetura RoSA.

A arquitetura consiste de um bloco reconfigurável acoplado a um processador hospedeiro. O bloco reconfigurável é composto por: células, banco de registradores, um gerenciador de configuração e um gerenciador de acesso à memória.

Figura 1. Diagrama de blocos de RoSA

## 2.1. Bloco Reconfigurável

As células correspondem a unidades reconfiguráveis que se comunicam através do banco de registradores. Cada célula possui unidades funcionais (UFs) que executam as operações lógicas e aritméticas, um banco de registradores local e um componente que realiza o controle.

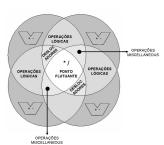

Para a disposição das unidades funcionais foi proposta uma metodologia baseada no reuso de hardware denominada RoSE (*Reuse-based Standard Datapath Architecture*), ilustrada na Figura 2.

Figura 2. Metodologia RoSE

De acordo com a metodologia, as UFs são organizadas em um caminho de dados baseado em quatro níveis de reusabilidade. Cada nível está relacionado com o grau de compartilhamento das operações entre as UFs e o custo das operações em hardware.

O primeiro nível de reusabilidade corresponde à área compartilhada entre as quatro UFs e representa as

operações mais custosas em hardware e/ou as menos usadas. As áreas compartilhadas entre três UFs correspondem ao segundo nível de reusabilidade e representam operações não usadas frequentemente e relativamente de baixo custo em hardware. O terceiro nível de reusabilidade consiste de operações consideradas pouco custosas em hardware e bastante utilizadas, sendo compartilhadas por duas unidades funcionais. Finalmente, o quarto nível de corresponde às operações reusabilidade frequentemente usadas e de baixo custo e estão presentes em todas as UFs.

A aplicação da metodologia permite o projeto da célula como um caminho de dados único, simplificando a comunicação entre as UFs e reduzindo área e custo das unidades, bem como das células.

A arquitetura RoSA possui quatro tipos de banco de registradores. O primeiro deles, denominado global, armazena as informações modificadas pelo processador apenas no início da execução da aplicação. Incluem-se nesse tipo os parâmetros das funções e as variáveis globais. O segundo tipo, denominado modificado, armazena os dados que são alterados pelo processador em tempo de execução. O terceiro tipo corresponde ao banco de registradores de saída e armazena as saídas das células. Por fim, o último tipo de banco de registradores é o local e armazena os cálculos intermediários realizados pelas UFs de cada célula.

O gerenciador de configuração é responsável por buscar a configuração na cache e distribuí-la entre as células.

A configuração de cada célula corresponde a uma palavra de instrução longa (120 bits). A configuração para toda a arquitetura é uma VLIW (do inglês *Very Long Instruction Word*) de 720 bits, que inclui a configuração das seis células.

O controle da célula tem a capacidade de receber a configuração e combiná-la com a arquitetura da célula, buscando os dados e executando as operações nas UFs correspondente.

O gerenciador de acesso à memória é responsável por atender as requisições de memória feitas pelas células. Esse componente recebe todas as requisições de leitura e escrita feitas pelas células e as armazena em uma fila de requisições. Essa abordagem evita incoerência entre os dados das células e da memória. Mais detalhes sobre a arquitetura podem ser encontrados em [5].

## 2.2. Processador

De acordo com Bondalapati e Prasanna [1], o processador hospedeiro é responsável dentre outras tarefas por: executar as funções de controle para configurar o bloco reconfigurável, escalonar os dados de entrada e saída e realizar a interface externa.

O processador também é responsável por selecionar os trechos que serão executados em paralelo (particionamento hardware/software). E por fim, indicar para a lógica reconfigurável o momento de executar.

Com tantas tarefas críticas a executar, a escolha de um processador adequado à arquitetura é uma decisão que influencia no resultado final. O processador hospedeiro deve atender a requisitos de desempenho, área e potência, de modo a se adequar aos requisitos da aplicação e do bloco reconfigurável. Além destes requisitos é preciso levar em consideração fatores tais como ferramentas disponíveis e compilador a ser utilizado.

Ferramentas e compilador influenciam na etapa de seleção dos trechos de código. É preciso avaliar as limitações de cada ferramenta e do próprio compilador para que não existam conflitos entre as técnicas escolhidas para a exploração de paralelismo e a disponibilidade dos recursos.

Por outro lado, muitas aplicações possuem restrições de tempo. A melhor escolha para atender essas restrições é, portanto, de um processador que combine desempenho, baixo consumo de potência e pequena área de hardware ocupada.

No trabalho aqui apresentado não foi possível, ainda, avaliar de modo combinado os requisitos de área, potência e desempenho. Entretanto, as próximas seções apresentam uma comparação entre o desempenho dos processadores SPARC V8 e Nios II. Para fins de comparação, algumas aplicações foram mapeadas para a arquitetura RoSA e executadas, os resultados de desempenho foram extraídos e analisados.

## 3. SPARC V8 X Nios II

O SPARC V8 (do inglês Scalable Processor ARChitecture Version 8), assim como a maioria dos microprocessadores modernos, é baseado em uma arquitetura RISC (do inglês Reduced Instruction Set Computer). As arquiteturas RISC apresentam um conjunto reduzido de instruções, porém com aproximadamente o mesmo desempenho de arquiteturas CISC (do inglês Complex Instruction Set Computer). No SPARC V8 esse conjunto é formado por 72 instruções básicas.

A Sun Microsystems projetou o SPARC em 1985, tendo como principais objetivos otimizar compiladores e facilitar a implementação de pipeline. Tais características, juntamente com o gerenciamento de janelas de registradores, provêem significativo desempenho ao processador SPARC V8 [3].

Semelhantemente ao SPARC V8, o processador Nios II baseia-se em uma arquitetura RISC composta por 94 instruções básicas. No seu projeto a Altera visou o oferecimento de maior flexibilidade aos seus FPGAs [4].

Nios II é um processador configurável, ao qual é possível adicionar novas instruções e periféricos. Além disso, o Nios II disponibiliza três opções de núcleo, cada qual com uma proposta de uso diferente: o Nios II/f (maior e mais rápido), o Nios II/s (padrão) e o Nios II/e (menor e menos rápido).

#### 4. Resultados

Essa seção apresenta uma avaliação de desempenho dos processadores SPARC V8 e Nios II para uma possível integração com a arquitetura RoSA

No que se refere ao SPARC V8, foi utilizada uma implementação em SystemC com precisão de ciclo. Quanto ao processador Nios II, foi utilizada sua configuração padrão (Nios II/s) e a ferramenta *Nios II Embedded Design Suite*.

Para efeito de comparação, foram coletados os tempos de execução de quatro aplicações em ambos os processadores: FFT (Transformada Rápida de Fourier, do inglês *Fast Fourier Transform*), sua inversa (IFFT - *Inverse Fast Fourier Transform*), codificação JPEG e DCT (Transformada Discreta de Cosseno, do inglês *Discrete Cosine Transform*). Os resultados obtidos são apresentados nas Tabelas 1 e 2.

Para calcular o tempo de execução das aplicações, tanto para o SPARC V8 quanto para o Nios II, foi utilizado o compilador cruzado (do inglês *cross-compiler*) do GCC.

O tempo total de execução das aplicações foi calculado em duas etapas. Inicialmente, foi calculado o tempo de execução de cada instrução a partir de uma ferramenta desenvolvida pela equipe. Em seguida, através de um perfil da aplicação (do inglês *profile*), utilizou-se o GCC para obter a quantidade de vezes que a mesma instrução foi executada.

Para avaliar o desempenho dos processadores na arquitetura reconfigurável, foi calculado o desempenho apenas dos trechos de código destinados ao processador (em ciclos). Esse resultado é apresentado na Tabela 1. Nessa tabela também é apresentada a diferença de desempenho (em porcentagem) entre o SPARC V8 e o Nios II.

Como é possível observar na Tabela 1, todas as medições realizadas sobre o processador Nios II

apresentam valores de tempo menores do que os do SPARC V8.

De acordo com a Tabela 1, para a arquitetura reconfigurável, o ganho de desempenho na utilização do Nios II para executar apenas os trechos da aplicação JPEG que não são paralelos é de 42,17% em comparação com o SPARC V8.

Tabela 1. Tempo de execução da parte destinada ao processador

| Aplicações | SPARCV8<br>(ciclos) | Nios II<br>(ciclos) | Diferença (%) |

|------------|---------------------|---------------------|---------------|

| DCT        | 21.232              | 14.764              | 30,46         |

| FFT        | 440.639             | 230.583             | 47,67         |

| IFFT       | 838.931             | 451.273             | 46,20         |

| JPEG       | 18.725              | 10.827              | 42,17         |

A Tabela 2 apresenta quanto o ganho de desempenho alcançado representa em toda a aplicação. A primeira coluna dessa tabela indica quanto a parte executada no processador representa de toda aplicação (em porcentagem). Essa informação foi obtida a partir de um estudo apresentado em [5].

De acordo com a tabela, o processador hospedeiro executa 63,57% da aplicação JPEG, os outros 36,43% são executados em paralelo no bloco reconfigurável. Portanto, um ganho de desempenho de 42,17% em 63,57% do código implica em um ganho de 26,8% no tempo de execução de toda aplicação (em comparação a execução do mesmo trecho no SPARC V8).

Tabela 2. Ganho de desempenho total

| Aplicações | Parte<br>seqüencial<br>(%) | Diferença<br>Nios X SPARC<br>(%) | Ganho de<br>desempenho<br>total (%) |

|------------|----------------------------|----------------------------------|-------------------------------------|

| DCT        | 26,07                      | 30,46                            | 7,94                                |

| FFT        | 17,11                      | 47,67                            | 8,15                                |

| IFFT       | 37,99                      | 46,20                            | 17,55                               |

| JPEG       | 63,57                      | 42,17                            | 26,8                                |

Os resultados obtidos são consequência de o Nios II possuir componentes mais velozes do que o SPARC V8. Dessa forma, de acordo com as restrições impostas pelas aplicações baseadas em fluxo de dados, é possível concluir que o processador mais adequado para a arquitetura reconfigurável RoSA é o Nios II da Altera.

Embora nesse artigo a comparação de desempenho tenha sido realizada apenas entre dois processadores, a estratégia utilizada para obter os resultados pode ser aplicada para qualquer conjunto de testes. Apenas deve-se considerar se existem compiladores cruzados para os processadores escolhidos.

#### 5. Conclusão

Esse artigo apresentou um estudo sobre o impacto que o processador hospedeiro causa no desempenho das arquiteturas reconfiguráveis híbridas.

A estratégia de avaliação apresentada pode ser aplicada a qualquer conjunto de processadores. Porém, no contexto deste trabalho as avaliações foram direcionadas aos processadores SPARC V8 da Sun Mycrosystems e o Nios II da Altera.

Como estudo de caso foi feita uma comparação do desempenho entre os dois processadores citados anteriormente. O objetivo da comparação é optar entre um dos dois processadores para anexá-lo à arquitetura reconfigurável RoSA.

Os resultados obtidos foram favoráveis à escolha do Nios II. Essa escolha foi feita com base em resultados experimentais que indicaram que os componentes do Nios II se mostraram mais velozes do que os do SPARC V8.

Os resultados do Nios II alcançaram ganho de desempenho de até 47,67% na execução seqüencial do trecho da aplicação destinado ao processador em comparação ao SPARC V8.

Com os resultados apresentados é possível perceber o quanto o processador hospedeiro influencia no desempenho total da arquitetura reconfigurável. Dessa forma, é de extrema importância escolher um processador adequado às restrições tanto das aplicações quanto da própria arquitetura.

#### 6. Referências

- [1] K. Bondalapati e V. K. Prasanna, "Reconfigurable Computing Systems", in Proceedings of the IEEE, Volume: 90, Issue: 7, IEEE Computer Society, Julho 2002, 1201-1217.

- [2] R. Hartenstein, "A Decade of Reconfigurable Computing: a Visionary Retrospective", in Proceedings of Design, Automation and Test in Europe, Munique, Alemanha, 13-16 Março 2001, IEEE Computer Society, 642-649.

- [3] Sun Microsystems, "The SPARC Architecture Manual: Version 8", http://www.sun.com, 2007.

- [4] Altera Corporation, "Nios II Processor Reference Handbook", http://www.altera.com, 2007.

- [5] M. M. Pereira, B. C. Oliveira e I. S. Silva, "RoSA: a Reconfigurable Stream-based Architecture," 20th Symposium on Integrated Circuits and Systems Design, Rio de Janeiro, Brasil, ACM Press, 2007.